# Single Phase Trasformerless Switched Capacitor Multi Level Inverter For Solar PV Applications

# P.Sathyanathan<sup>1</sup>, P.Usha Rani<sup>2</sup>, Promod Ranjan Debnath<sup>3</sup>

VEL TECH Rangarajan Dr Sagunthala RD Institute of science and Technology, Chennai $^{1,3},$  R.M.D Engineering College, Chennai $^2$

Corresponding author: Promod Ranjan Debnath, Email: vtp2768@veltech.edu.in

Multilevel inverters (MLIs) have been proposed for the purpose of increase power level and to improve the power factor and total harmonic distortion (THD) in comparison with conventional two-level inverters. This technological advancement helps to achieve high performance and low cost, transformer less multi-level inverters which may commonly exploited in grid tied Photovoltaic (PV) generating systems. The application areas of MLIs are residential use in uninterruptible power supplies (UPSs); All these applications require increased reliability in terms of lower switching losses, increased power factor, and low total harmonic distortion (THD) for ensuring robust and smooth operation. Selection of control strategy for MLIs is one of the important aspects while designing of MLI. SPWM (Sinusoidal pulse width modulation) technique has been selected and same is used in the proposed transformer less switch capacitor based MLIs. SPWM which is based on comparing the modulating and carrier signal for generating the switching pulses, is the fundamental switching and control strategy generally used in MLI control. The PWM method used to control the switching sequences of inverters is directly responsible for controlling the output waveforms of current and voltage, while defining the efficiency of the inverter by managing the switching losses and THD ratios. This paper proposes high efficient nine level, eleven level, thirteen level fifteen level switched capacitor-based inverter. Further total harmonic distortion for each level has been calculated using MATLAB simulation and the value observed for the same is compared for each level of MLI.

**Keywords**: Total harmonic distortion (THD), Sinusoidal pulse width modulation (SPWM), Transformer lessswitched capacitor multilevel inverter (TSCMLI), Photo voltaic (PV).

2023. In Saroj Hiranwal & Garima Mathur (eds.), Artificial Intelligence and Communication Technologies, 789–806. Computing & Intelligent Systems, SCRS, India. https://doi.org/10.52458/978-81-955020-5-9-74

#### 1 Introduction

The paper is based on single phase switched capacitor based multi-level inverter topologies which is being used for Photovoltaic (PV) applications for domestic usage. The proposed topology is able to mitigate the leakage current and facilitating continuous Grid frequency voltage. It does not have transformer which is being used for galvanic isolation between load and source. Hence it is more cost effective, efficient and not bulky is in size. The control strategies used is based on sinusoidal PWM (SPWM). A distinctive aspect of MLI 100% DC bus utilization is achieved. In this proposed paper nine level, eleven level, thirteen level and fifteen level inverter have been designed using power electronic MOSFET switches for higher frequency application. Simulation is done using MATLAB 2021a and Total Harmonic Distortion (THD) is measured for all the above level Multi level Inverter.

Transformer less multilevel inverters are attracting lot of popularity, especially for solar PV application. this is because the elimination of transformer, which is bulky component, leads toreduction of the size, wight and cost of the system. Apart from this transformer less system improves the system efficiency as transformer contributes to significant amount of copper and Iron loss. Existing system has used 5 level Inverter where 06 no power electronics switches are being used in H8 topologies. The existing circuit as per reference paper is also simulated using MATLAB and THD for the same has been measured for taking reference. Power electronic switch IGBT was used in existing system and one of the drawbacks is TSC5LI topology can not be upgraded to for higher level.

#### 2. Matlab Simulation Circuit of Existing System

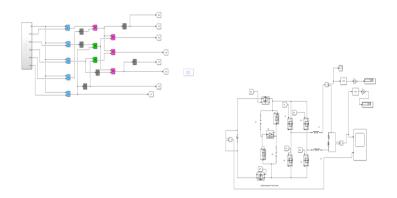

Fig. 1: Circuit diagram of existing system

#### 3. Proposed System

The proposed Nine level inverter comprises of seven power electronic switch MOSFET. Four switches are connected in H bridge configuration and three switches are connected for level generation. R or R-L load is connected parallel to the H – bridge and input DC voltage is connected to the series of level generation. The inverter utilizes the operation in nine exchanging/ switching states constituted by the SPWM system. The proposed inverter is being simulated using MATLAB.

#### 3.1 Control Strategies For Proposed Multilevel Inverter

**3.1.1 Sinusoidal Pulse Width Modulation (SPWM)**: The most widely used fundamental switching frequency methods are selective harmonic elimination PWM (SHE-PWM), space vector PWM (SVM), angle calculation, and nearest level control methods. While SHE-PWM and SVM are used in high-frequency switching, sinusoidal PWM (SPWM) is another widely used method in this category. The carrier-based PWM methods are operated in open loop without any feedback signal or in closed-loop current control, where the load current is used as triggering feedback in the modulator. This is the most commonly used method for inverter application. A carrier wave is compared with Sine wave of operating frequency for generating the SPWM signal.

**3.1.2 Multi level Inverter Operational Parameter:** Multi-level inverter attracts industry due to its low cost, easy to deigned, flexible power level. One of the operational parameters Of MLI is Total Harmonic Distortion (THD). As The level of MLI increases the no of switch also increases which further enhances the switching losses. On the other hand, increasing level increases the power and decreases the Total Harmonic Distortion (THD).

**3.1.3 Total Harmonic Distortion (THD):** The total harmonic distortion is a common measure of signal harmonic level causing distortion at voltage or current level. It is referred as the ratio of total harmonics to that value at the fundamental frequency. It is usually given in percentage.

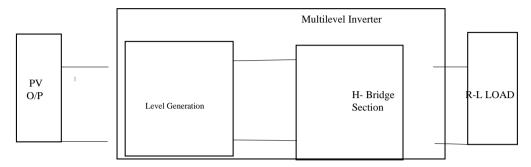

# 4. Proposed Block Diagram for Nine Level Inverter

Fig.2: Block diagram of proposed nine level inverter

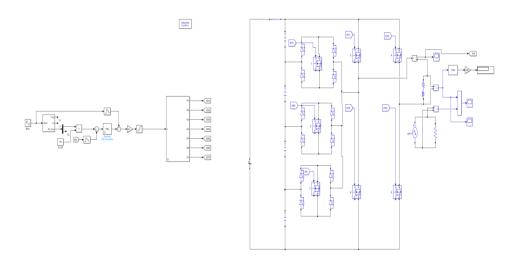

5. Matlab Simulation Circuit Diagram for Proposed Nine Level Inverter

Fig.3: Circuit Diagram of Nine Level Inverter

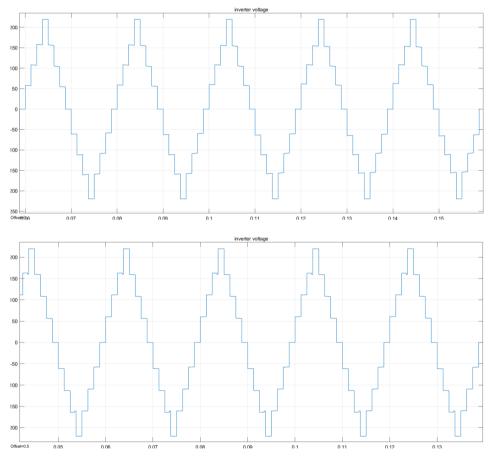

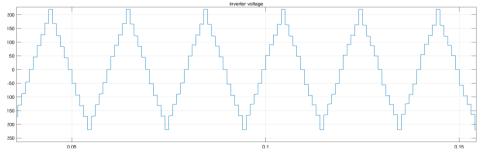

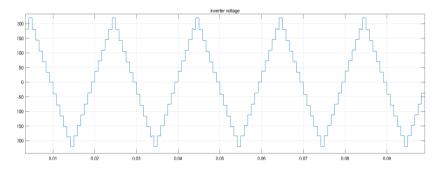

# 6 Output Voltage Waveform of Proposed Nine Level Inverter with R & R-L Load

The output voltage wave form of proposed nine level with R and R-L load is illustrated in fig.4 below.

Fig. 4: Output voltage waveform of Nine Level Inverter

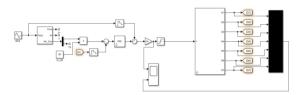

#### 7. Control Strategy Closed Loop SPWM Used for Proposed Inverter

Discrete 1e-06 s.

The control strategy used for proposed inverter is given in fig. 5 below.

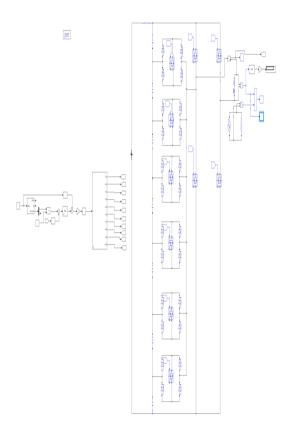

Fig.5: Control Circuit for generation of Gate pulse for Power Electronics Switch MOSFET

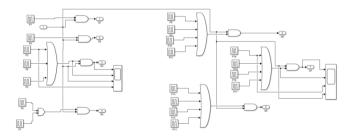

#### 8. Control Strategy Subsystem

The control strategy subsytem is given below fig.6.

Fig. 6 :Control Circuit for Subsystem for Gate pulse for Power Electronics Switch MOSFET

**8.1 Switching States:** Switching states of proposed inverter is described in table cited below for generation PWM signal.

| Vo      | <b>S1</b> | <b>S2</b> | <b>S</b> 3 | <b>S</b> 4 | <b>S</b> 5 | <b>S6</b> | <b>S</b> 7 |

|---------|-----------|-----------|------------|------------|------------|-----------|------------|

| 4V      | 1         | 0         | 0          | 1          | 0          | 0         | 0          |

| $_{3V}$ | 0         | 0         | 0          | 1          | 1          | 0         | 0          |

| 2V      | 0         | 0         | 0          | 1          | 0          | 1         | 0          |

| V       | 0         | 0         | 0          | 1          | 0          | 0         | 1          |

| 0       | 1         | 0         | 1          | 1          | 0          | 0         | 0          |

| 0       | 0         | 1         | 0          | 0          | 0          | 0         | 0          |

| -V      | 0         | 1         | 0          | 0          | 1          | 0         | 0          |

| -2V     | 0         | 1         | 0          | 0          | 0          | 1         | 0          |

| -3V     | 0         | 1         | 0          | 0          | 0          | 0         | 1          |

| -4V     | 0         | 1         | 1          | 0          | 0          | 0         | 0          |

Table. 1: Switching states of proposed nine level inverter

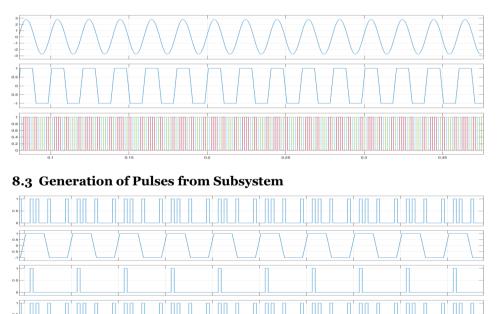

#### 8.2 Generation of Switching Pulse

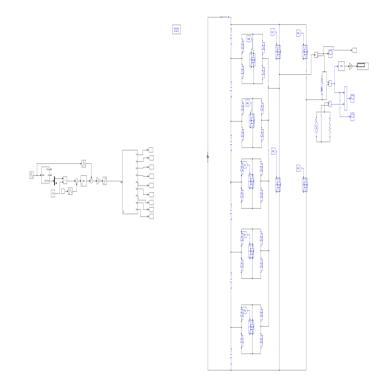

#### 8.4 Simulation Circuit Diagram of Proposed Eleven Level Inverter

The circuit diagram of proposed eleven level inverter is illustrated in fig.7 below

Fig. 7 :Circuit Diagram of Eleven level Inverter

**8.5Proposed 11 Level Inverter**: The propose model has total eight power electronics switch MOSFET. The proposed model can be utilized for 11, 13 & 15 level to generate AC waveform close to sine wave.

**8.6 Control Strategy:** Similar Control strategy like nine level inverter is being used for eleven level, thirteen level and fifteen level inverters.

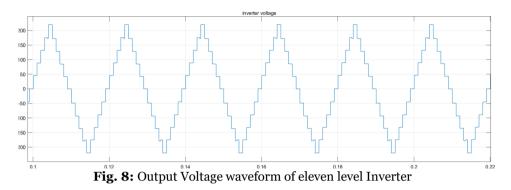

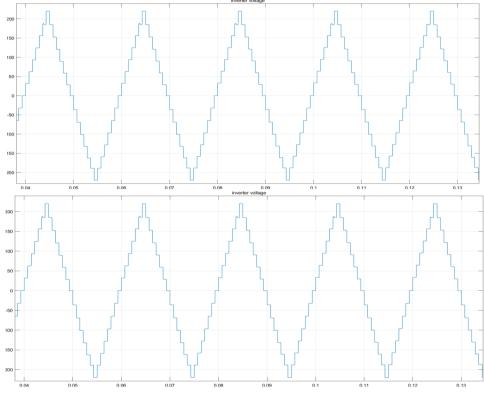

# 8.7 Output Voltage Waveform for Proposed Eleven Level Inverter with R & R-L Load

The output voltage waveforms of proposed eleven level inverter for R and R-L load are given below.

796

**8.8 Switching States**: Switching states of proposed eleven level inverter is described in table cited below for generation PWM signal.

| Vo      | <b>S1</b> | <b>S2</b> | <b>S</b> 3 | <b>S</b> 4 | <b>S</b> 5 | <b>S6</b> | <b>S</b> 7 | <b>S8</b> |

|---------|-----------|-----------|------------|------------|------------|-----------|------------|-----------|

| V       | 0         | 0         | 0          | 1          | 1          | 0         | 0          | 0         |

| 2V      | 0         | 0         | 0          | 1          | 0          | 1         | 0          | 0         |

| $_{3}V$ | 0         | 0         | 0          | 1          | 0          | 0         | 1          | 0         |

| 4V      | 0         | 0         | 0          | 1          | 0          | 0         | 0          | 1         |

| 5V      | 1         | 0         | 0          | 1          | 0          | 0         | 0          | 0         |

| 4V      | 0         | 0         | 0          | 1          | 0          | 0         | 0          | 1         |

| 3V      | 0         | 0         | 0          | 1          | 0          | 0         | 1          | 0         |

| 2V      | 0         | 0         | 0          | 1          | 0          | 1         | 0          | 0         |

| V       | 0         | 0         | 0          | 1          | 1          | 0         | 0          | 0         |

| 0       | 0         | 0         | 1          | 1          | 0          | 0         | 0          | 0         |

| -V      | 0         | 1         | 0          | 0          | 0          | 0         | 0          | 1         |

| -2V     | 0         | 1         | 0          | 0          | 0          | 0         | 1          | 0         |

| -3V     | 0         | 1         | 0          | 0          | 0          | 1         | 0          | 0         |

| -4V     | 0         | 1         | 0          | 0          | 1          | 0         | 0          | 0         |

| -5V     | 0         | 1         | 1          | 0          | 0          | 0         | 0          | 0         |

| -4V     | 0         | 1         | 0          | 0          | 1          | 0         | 0          | 0         |

| -3V     | 0         | 1         | 0          | 0          | 0          | 1         | 0          | 0         |

| -2V     | 0         | 1         | 0          | 0          | 0          | 0         | 1          | 0         |

| -V      | 0         | 1         | 0          | 0          | 0          | 0         | 0          | 1         |

| 0       | 0         | 0         | 1          | 1          | 0          | 0         | 0          | 0         |

Table. 2: Switching states of proposed eleven level inverter

#### 8.9 Simulation Circuit Diagram Thirteen Level Inverter

Fig.9: Circuit Diagram of thirteen level Inverter

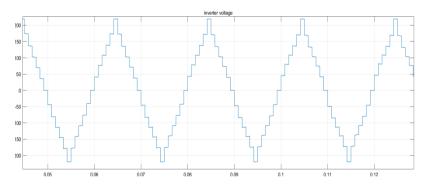

#### 8.10 Output Voltage Waveform with R and R-L Load

Fig. 10: Output Voltage waveform of thirteen level inverter

The proposed thirteen level inverter has nine power electronics switches. Four are connected in H- bridge and remaining five are being used for level generation. Similar closed loop SPWM control strategy like nine level is being used for generation of SPWM pulses.

**8.11 Switching States**: Switching states of proposed thirteen level inverter is described in table cited below for generation PWM signal

| Vo         | <b>S</b> 1 | S2 | <b>S</b> 3 | <b>S</b> 4 | <b>S</b> 5 | <b>S6</b> | <b>S</b> 7 | <b>S8</b> | <b>S</b> 9 |

|------------|------------|----|------------|------------|------------|-----------|------------|-----------|------------|

| <b>6</b> V | 1          | 0  | 0          | 1          | 0          | 0         | 0          | 0         | 0          |

| 5V         | 0          | 0  | 0          | 1          | 0          | 0         | 0          | 0         | 1          |

| 4V         | 0          | 0  | 0          | 1          | 0          | 0         | 0          | 1         | 0          |

| 3V         | 0          | 0  | 0          | 1          | 0          | 0         | 1          | 0         | 0          |

| 2V         | 0          | 0  | 0          | 1          | 0          | 1         | 0          | 0         | 0          |

| V          | 0          | 0  | 0          | 1          | 1          | 0         | 0          | 0         | 0          |

| 0          | 0          | 0  | 1          | 1          | 0          | 0         | 0          | 0         | 0          |

| 0          | 0          | 0  | 1          | 1          | 0          | 0         | 0          | 0         | 0          |

| -V         | 0          | 1  | 0          | 0          | 0          | 0         | 0          | 0         | 1          |

| -2V        | 0          | 1  | 0          | 0          | 0          | 0         | 0          | 1         | 0          |

| -3V        | 0          | 1  | 0          | 0          | 0          | 0         | 1          | 0         | 0          |

| -4V        | 0          | 1  | 0          | 0          | 1          | 0         | 0          | 0         | 0          |

| -5V        | 0          | 1  | 0          | 0          | 1          | 0         | 0          | 0         | 0          |

| -6V        | 0          | 1  | 1          | 0          | 0          | 0         | 0          | 0         | 0          |

Table. 3: Switching states of proposed thirteen level inverter

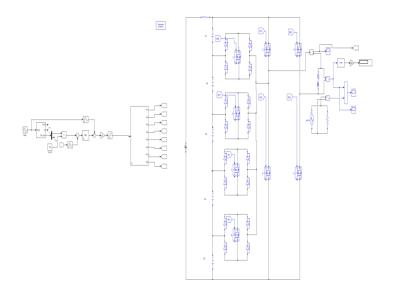

#### 9. Simulation Diagram of Proposed Fifteen Level Inverter

It comprises of ten power electronic switch MOSFET as shown in fig. 11. Four are connected in H- bridge and six are connected for level generation. Similar closed loop SPWM technique is being used for generation of SPWM pulses.

Fig.11 :Circuit Diagram of Fifteen Level Inverter

#### 10. Output Voltage Waveform of Fifteen Level Inverter with R and R-L Load

Fig. 12: Output voltage waveform of Fifteen Level Inverter

#### **11.** Switching States

Switching states of proposed thirteen level inverter is described in table cited below for generation PWM signal

| Vo | <b>S1</b> | <b>S2</b> | <b>S</b> 3 | <b>S</b> 4 | <b>S</b> 5 | <b>S6</b> | <b>S</b> 7 | <b>S8</b> | <b>S9</b> | <b>S10</b> |

|----|-----------|-----------|------------|------------|------------|-----------|------------|-----------|-----------|------------|

| 7V | 1         | 0         | 0          | 1          | 0          | 0         | 0          | 0         | 0         | 0          |

| 6V | 0         | 0         | 0          | 1          | 0          | 0         | 0          | 0         | 0         | 1          |

| 5V | 0         | 0         | 0          | 1          | 0          | 0         | 0          | 0         | 1         | 0          |

| 4V | 0         | 0         | 0          | 1          | 0          | 0         | 0          | 1         | 0         | 0          |

| 3V | 0         | 0         | 0          | 1          | 0          | 0         | 1          | 0         | 0         | 0          |

Table 4: Switching states of proposed fifteen level inverter

P.Sathyanathan<sup>1</sup>, P.Usha Rani<sup>2</sup>, Promod Ranjan Debnath<sup>3</sup>

| 2V  | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 |

|-----|---|---|---|---|---|---|---|---|---|---|

| V   | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0   | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0   | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| -V  | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| -2V | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| -3V | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| -4V | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| -5V | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| -6V | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| -7V | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

# 12. Component Used During MATLAB Simulation

| level<br>of | Sinus<br>oidal<br>Signal | Load<br>R | Load<br>L | No of<br>MOSF | No of<br>Diode | DC<br>Voltag | C<br>Valu | PID   |

|-------------|--------------------------|-----------|-----------|---------------|----------------|--------------|-----------|-------|

| 9           | 50                       | 10        | 100       | 0             | 12             | 220          | 10        | Kp=10 |

| Level       |                          |           |           | 7             |                |              |           | 0     |

|             |                          |           |           |               |                |              |           | Ki=20 |

|             |                          |           |           |               |                |              |           | 0     |

|             |                          |           |           |               |                |              |           | Kd=0  |

| 11          | 50                       | 10        | 100       | 0             | 16             | 220          | 10        | Кр=10 |

| Level       |                          |           |           | 8             |                |              |           | 0     |

|             |                          |           |           |               |                |              |           | Ki=20 |

|             |                          |           |           |               |                |              |           | 0     |

|             |                          |           |           |               |                |              |           | Kd=0  |

| 13          | 50                       | 10        | 100       | 0             | 20             | 220          | 10        | Кр=10 |

| Level       |                          |           |           | 9             |                |              |           | 0     |

|             |                          |           |           |               |                |              |           | Ki=20 |

|             |                          |           |           |               |                |              |           | 0     |

**Table. 5**: Value of component used during simulation

|       |    |    |     |   |    |     |    | Kd=0  |

|-------|----|----|-----|---|----|-----|----|-------|

| 15    | 50 | 10 | 100 | 1 | 24 | 220 | 10 | Kp=10 |

| level |    |    |     | 0 |    |     |    | 0     |

|       |    |    |     |   |    |     |    | Ki=20 |

|       |    |    |     |   |    |     |    | 0     |

|       |    |    |     |   |    |     |    | Kd=0  |

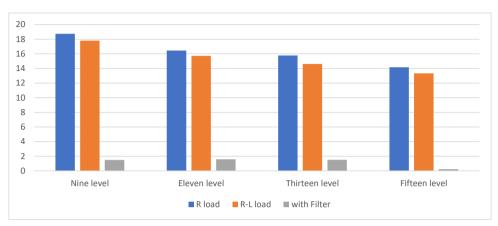

### 13. Results / Analysis

The analysis is carried out based on the simulation results observed in nine, eleven, thirteen and fifteen level inverter. The THD are measured for each level both for R and R-L load and analysis of all the multilevel inverter is carried out.

#### (i) Comparison of THD Amongst Nine, Eleven, Thirteen and Fifteen Level Inverter

| Sr<br>No | Level of<br>MLI | THD<br>measured<br>Using | THDwithπFiltermeasuredUsingMATLAB | Remarks               |

|----------|-----------------|--------------------------|-----------------------------------|-----------------------|

|          |                 | MATLAB<br>Simulink       | Simulink                          |                       |

| 1        | Nine level      | Current:3.686            | Current: 0.508                    | In comparison with    |

|          |                 | Voltage:17.81            | Voltage:1.483                     | 5 level Inverter, The |

|          |                 |                          |                                   | Total Harmonic        |

|          |                 |                          |                                   | level is decreasing   |

| 2        | Eleven          | Current:3.314            | Current: 0.543                    | Harmonic              |

|          | level           | Voltage:15.66            | Voltage:1.571                     | Decreasing            |

| 3        | Thirteen        | Current:                 | Current: 0.516                    | Harmonic              |

|          | Level           | 3.034                    | Voltage:1.504                     | Decreasing            |

|          |                 | Voltage:14.29            |                                   |                       |

| 4        | Fifteen         | Current :3.13            | Current:0.22                      | Harmonic              |

|          | Level           | Voltage :13.26           | Voltage :0.22                     | Decreasing            |

Table. 6: Comparison of THD

#### 14. Conclusions

A new switched-mode multilevel inverter, which is derived from conventional multilevel inverter, has been introduced. The proposed model of nine, eleven, thirteen and fifteen level inverter are designed for better efficiency and performance using MATLAB 2021a Simulink. The proposed multilevel inverters are transformer less, so the losses due iron & copper losses are restricted. The Total Harmonic Distortion for each level was measured and compared with next level both for R and R-L load. Control strategy, SPWM is being used for proposed multilevel inverter. Further, close loop control strategy has been used for better performance and to mitigate the harmonics. PID controller with gain (vizKp =100, Ki = 200 &Kd=0) is also used in closed loop control circuit for calculating present, past and future error and accordingly amplify the error signal. Apart from this, THD value of all the above multilevel inverter are measured based on R , R-L Load at the output of the inverter. The observed values during simulation are tabulated below for reference. It is concluded that as level of MLI is increased, the THD is decreased accordingly.

| Sr<br>No | Level<br>of MLI   | THD<br>measured<br>Using<br>MATLAB<br>Simulink | THD<br>measured<br>Using<br>MATLAB<br>Simulink with | THD with π<br>Filter (R-L<br>load)<br>measured<br>Using | Final<br>results                            |

|----------|-------------------|------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------|---------------------------------------------|

|          |                   | with R load                                    | R-L load                                            | MATLAB<br>Simulink                                      |                                             |

| 1        | Nine<br>level     | Current:18.75<br>Voltage:18.75                 | Current:3.686<br>Voltage:17.81                      | Current:<br>0.508<br>Voltage:1.483                      | Decreasing<br>as Compared<br>to Five level. |

| 2        | Eleven<br>level   | Current:16.45<br>Voltage:16.45                 | Current:3.314<br>Voltage:15.66                      | Current:<br>0.543<br>Voltage:1.571                      | Deceasing                                   |

| 3        | Thirteen<br>Level | Current:15.78<br>Voltage:15.78                 | Current:<br>3.034<br>Voltage:14.29                  | Current:<br>0.516<br>Voltage:1.504                      | Decreasing                                  |

| 4        | Fifteen<br>Level  | Current:14.17<br>Voltage:14.17                 | Current :3.13<br>Voltage :13.26                     | Current:0.22<br>Voltage :0.22                           | Decreasing                                  |

Table. 7: Comparison of THD

Fig 13: THD Vs level of MLI for R, R-L load & with filter

# 15. Discussions

This paper is to provide technical information in details regarding circuit design of TSCMLI viz. 9 level, 11 level, 13 level and 15 level, control strategy namely closed loop SPWM used for generating various level and how it works to generate level with the help of proper feedback from output current of respective MLI. Moreover, THD w.r.t 'R' and 'RL' load have been calculated for all respective MLI and same was compared. Further, THD value has also been calculated for all level of inverter by connecting C-L-C filter before the loadresulting which improve the THD.

This paper is also encouraged for the scope of future study on aspects likepower quality, power factor and reactive power for MLI.

# 16. Acknowledgement

This project is carried out in the Modernized Power Electronics and Drives Laboratory at Vel Tech Rangarajan Dr. Sagunthala R&D Institute of Science and Technology, Chennai.

This Laboratory is funded by AICTE MODROB scheme 2019-2020.

#### References

- A review of single-phase grid-connected inverters for photovoltaic modulesIEEE Transactions on Industry Applications, vol. 41, no. 5, pp. 1292-1306, Sep.-Oct. 2005.B. Kjaer, J. K. Pedersen and F. Blaabjerg

- [2] Implementation of Active NPC Circuits in Transformer-Less Single-Phase InverterWith Low Leakage CurrentIEEE Transactions on Industry Applications, vol. 53, no. 6, pp. 5658-5667, Nov.-Dec. 2017L. Zhou, F. Gao and T. Xu

- [3] Performance Evaluation of a Three-Level ANPC Photovoltaic Grid-ConnectedInverter With 650-V SiC Devices and Optimized PWMIEEE Transactions on IndustryApplications, vol. 52, no. 3, pp. 2475-2485, May-June 2016.D. Barater, C. Concari, G. Buticchi, E. Gurpinar, D. De and A. Castellazzi

- [4] A new Family of 1phase five level Transformer less Inverter for solar PVApplicationG VeeraBharath, Students Member IEEE, ArpanHota, Students Member, IEEE andVivekAgarwal Fellow, IEEE

- [5] A TRANSFORMERLESS GRID CONNECTED TO PV SYSTEM BASED ON HERICINVERTERB Loveswara Rao1, D Swathi2, P Viswa Teja3, V Sai Pranay4 1,2,3,4Department of electrical and Electronics Engineering, KoneruLakshmaiah Education Foundation, Vaddeswaram, AP, India.

- [6] Past, present and future of grid connected photovoltaic- and hybrid-power- systemsIEEE Power Engineering Society Summer Meeting, Seattle, WA, 2000, vol. 2., pp. 1283-1288, Jul. 2000.M. Meinhardt and G. Cramer

- [7] International Journal of Innovative Research in Electrical, Electronics, Instrumentation and ControlEngineering Vol. 7, Issue 2, February 2019 Copyright to IJIREEICE DOI 10.17148/IJIREEICE.2019.7213 63 Switched Capacitor Based Multilevel Inverter Topology Compatible with Multiple Inputs Sajina S1, Frieda Mohan2 PG Scholar, Department of EEE, Govt. Engg., College Barton Hill, Thiruvananthapuram, India Assistant Professor, Department of EEE, Govt. Engg., College Barton Hill, Thiruvananthapuram, India

- [8] International Journal of Engineering and Advanced Technology (IJEAT) ISSN:2249 8958, Volume-9 Issue-4, April 2020THD Reduction in Multi-Level Inverters based on Multicarrier Pulse Width ModulationTechnique, Kishore B, Senbakaraj, Periyasamy, Poongkabila

- [9] Review Review of Multilevel Inverters for PV Energy System ApplicationsAli Bughneda 1, Mohamed Salem 1,\*, Anna Richelli 2,\*, DahamanIshak 1 and Salah Alatai

- [10] Reduction of Common-Mode Voltages for Five-Level Active NPC Inverters by Space Vector Modulation TechniqueQuocAnh Le Student Member, IEEE Yeungnam University 280 Deahak-Ro, Gyeongsan, Gyeongbuk, Korea lequocanh@ctu.edu.vn Dong-Choon Lee SeniorMember, IEEE Yeungnam University 280 Deahak-Ro, Gyeongsan, Gyeongbuk, Korea

- [11] A high performance multi-level inverter with reduced power electronics DevicesArticle in international Journal of Power electronics and drive system – Dec 2020Author: Hur Jedi, University of kufaAbnanSabbbar, University of Kufa

- [12] Reduction of Total Harmonic Distortion in Cascaded H-Bridge Inverter byPattern Search TechniqueSuresh N. and R. Samuel Rajesh BabFaculty of Electrical and Electronics Engineering, Sathyabama University and Associate Professor, Departement of Electronics and Instrumentation Engineering, Sathyabama University The following text books are also referred during the project work;

- [13] Text Book on Multilevel Inverters Control Methods and Advanced PowerElectronic Applications, Edited by ErsanKabalcı Department of Electrical and Electronics Engineering, Faculty of Engineering and Architecture, NevsehirHaciBektasVeli University, Nevsehir, Turkey

- [14] Text Book on Multi level InvertersConventional & Emerging Topologies and their control. Shri Krishna Kumar Gupta, PhD, MIEEE, PallaveeBhatnagar, PhD, MIEEE